## YAMAHA L S I

# **YMF264**

## (OPNC) FM Operator type-N CMOS

#### ■概要

YMF264(OPNC)は、NMOSプロセスLSIのYM2203(OPN)とレジスタコンパチブルのCMOSプロセスLSIです。

FM方式の音源と矩形波を制御するSSG(PSG)タイプの音源を持っており、それぞれ自由に音色設定のできるように、独立したレジスタアレーがあります。このレジスタに音色情報を入力するだけで、楽音・効果音などの音を発音することができます。この2つの音源はそれぞれ3音(3チャンネル)ずつ、楽音発生が可能であるため、ミュージックシンセサイザーとしての機能を持ち、自然楽器はもちろんのこと、幅広い音色を作ることが可能です。

#### ■特徴

- YM2203(OPN)とレジスタコンパチブル。

- ・FM方式の音源を採用し、3音同時発音が可能。

- FM3音のうち1音については、特殊な効果音が発音可能。

- ・2つのタイマー内蔵。

- FM方式以外に矩形波音3音及びホワイトノイズを発生。

- ・2つの8ビット汎用I/Oポート内蔵。

- クロック分周器内蔵により、動作周波数領域が広い。

- ・入出力はTTLコンパチブル。

- · Si-Gate CMOS-LSI.

- 単-5V電源

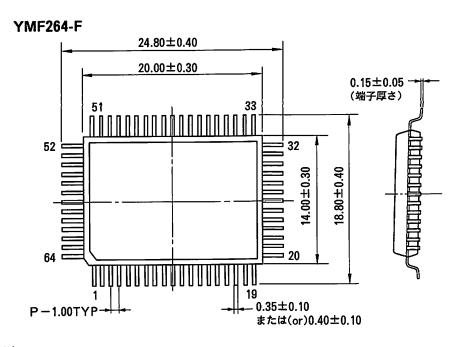

- 64ピン プラスチックQFP(YMF264-F)

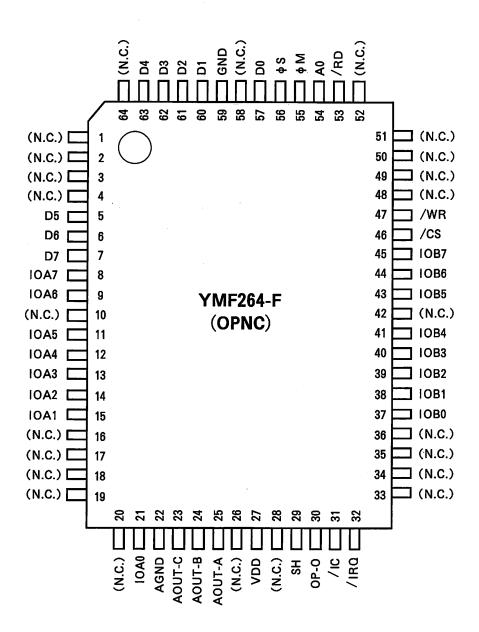

#### ■端子配置図

64pin QFP top view

## ■端子機能説明

| No. | 端子名    | I/O  | 機                 | 能        |

|-----|--------|------|-------------------|----------|

| 1   | (N.C.) |      | *                 |          |

| 2   | (N.C.) |      | *                 |          |

| 3   | (N.C.) |      | *                 |          |

| 4   | (N.C.) |      | *                 |          |

| 5   | D5     | I/O  | CPUインターフェース データバス |          |

| 6   | D6     | I/O  | CPUインターフェース データバス | ス(D6)    |

| 7   | D7     | I/O  | CPUインターフェース データバス | ス(D7)    |

| 8   | IOA7   | I+/O | 汎用I/Oポート-A        |          |

| 9   | IOA6   | I+/0 | 汎用I/Oポート-A        |          |

| 10  | (N.C.) |      | *                 |          |

| 11  | IOA5   | I+/O | 汎用I/Oポート-A        |          |

| 12  | IOA4   | I+/O | 汎用I/OポートーA        |          |

| 13  | IOA3   | I+/0 | 汎用I/Oポート-A        |          |

| 14  | IOA2   | I+/0 | 汎用I/Oポート-A        |          |

| 15  | IOA1   | I+/0 | 汎用I/Oポート-A        |          |

| 16  | (N.C.) |      | *                 |          |

| 17  | (N.C.) |      | *                 |          |

| 18  | (N.C.) |      | *                 |          |

| 19  | (N.C.) |      | *                 |          |

| 20  | (N.C.) |      | *                 |          |

| 21  | IOA0   | I+/O | 汎用I/Oポート-A        |          |

| 22  | AGND   |      | アナログ部グランド         |          |

| 23  | AOUT-C | SF   | SSG Cチャンネル音声出力    |          |

| 24  | AOUT-B | SF   | SSG Bチャンネル音声出力    |          |

| 25  | AOUT-A | SF   | SSG Aチャンネル音声出力    |          |

| 26  | (N.C.) |      | *                 |          |

| 27  | VDD -  | _    | +5V電源             |          |

| 28  | (N.C.) |      | *                 |          |

| 29  | SH     | 0    | DACインターフェース サンプル: | ホールド信号出力 |

| 30  | OP-O   | 0    | DACインターフェース FM音声信 | 言号出力     |

| 31  | /IC    | I+   | イニシャルクリア入力        |          |

| 32  | /IRQ   | OD   | 割り込み信号出力          |          |

| 33  | (N.C.) |      | *                 |          |

| 34  | (N.C.) |      | *                 |          |

| 35  | (N.C.) |      | *                 |          |

| 36  | (N.C.) |      | *                 |          |

| 37  | IOB0   | I+/0 | 汎用I/Oポート-B        |          |

| 38  | IOB1   | I+/0 | 汎用I/Oポート-B        |          |

| 39  | IOB2   | I+/0 | 汎用I/Oポート-B        |          |

| 40  | IOB3   | I+/0 | 汎用I/Oポート-B        |          |

| 41  | IOB4   | I+/0 | 汎用I/Oポート-B        |          |

| 42  | (N.C.) |      | *                 |          |

| No. | 端子名      | I/O  | 機           | 能          |

|-----|----------|------|-------------|------------|

| 43  | IOB5     | I+/0 | 汎用I/OポートーB  | •          |

| 44  | IOB6     | I+/0 | 汎用I/Oポート-B  |            |

| 45  | IOB7     | I+/0 | 汎用I/Oポート-B  |            |

| 46  | /CS      | I+   | CPUインターフェース | チップセレクト信号  |

| 47  | /WR      | I    | CPUインターフェース | ライトイネーブル信号 |

| 48  | (N.C.)   |      | *           |            |

| 49  | (N.C.)   |      | *           |            |

| 50  | (N.C.)   |      | *           |            |

| 51  | (N.C.)   |      | *           |            |

| 52  | (N.C.)   |      | *           |            |

| 53  | /RD      | I    | CPUインターフェース | リードイネーブル信号 |

| 54  | A0       | I    | CPUインターフェース | アドレス選択信号   |

| 55  | $\phi$ M | I    | マスタークロック入力  |            |

| 56  | φS       | 0    | DACインターフェース | ビットクロック出力  |

| 57  | D0       | I/O  | CPUインターフェース | データバス(D0)  |

| 58  | (N.C.)   |      | *           |            |

| 59  | GND      | _ I  | デジタル用グランド   |            |

| 60  | D1       | I/O  | CPUインターフェース | データバス(D1)  |

| 61  | D2       | I/O  | CPUインターフェース | データバス(D2)  |

| 62  | D3       | I/O  | CPUインターフェース | データバス(D3)  |

| 63  | D4       | I/O  | CPUインターフェース | データバス(D4)  |

| 64  | (N.C.)   |      | *           |            |

注) (N.C.): この端子は通常無接続でご使用下さい。

I+:プルアップ抵抗内蔵入力端子

I+/O:プルアップ抵抗内蔵入出力端子

OD:オープンドレイン出力端子

SF:ソースフォロワ出力端子

## ■機能説明

## 1. レジスタマップ

(a) FM部レジスタ(ライト専用)

| address   |                                                  | Register    |              | Comment                                    |  |  |  |

|-----------|--------------------------------------------------|-------------|--------------|--------------------------------------------|--|--|--|

| (HEX)     | d7 d6 d5                                         | d4 d3       | d2 d1 d0     |                                            |  |  |  |

| 21        |                                                  | TEST        |              | LSIのTESTデータ                                |  |  |  |

| 24        |                                                  | TIMER-A     | - I-13 4ED A | TIMER-Aの上位 8 ビット                           |  |  |  |

| 25        |                                                  | TIMED D     | TIMER-A      | TIMER-Aの下位 2 ビット<br>TIMER-Bのデータ            |  |  |  |

| 26        | MODE                                             | TIMER-B     | BLE LOAD     | 3CHのモード及びTIMER-A/Bのコントロール                  |  |  |  |

| 27<br>28  | MODE R                                           | ESET ENA    | CH           | Key-on/off                                 |  |  |  |

| 2D        | 3201                                             |             |              | プリスケーラをセット                                 |  |  |  |

| 2E        |                                                  |             |              | 1/3, 1/6分周の選択                              |  |  |  |

| 2F        |                                                  |             |              | 分周器を1/2分周にセット                              |  |  |  |

| 30        |                                                  |             |              |                                            |  |  |  |

| ;         | DT                                               |             | MULTI        | Detune/Multiple<br>(33, 37, 3Bのaddressは無し) |  |  |  |

| 3E        |                                                  |             |              | (33, 37, SDV) addressia m U7               |  |  |  |

| 40        |                                                  | <u></u> .   |              | Total Level                                |  |  |  |

| :         | /                                                | TL          |              | (43, 47, 4Bのaddressは無し)                    |  |  |  |

| 4E        | <u>/</u>                                         |             |              | (40, 47, 42004410001071107                 |  |  |  |

| 50        |                                                  | Λ           |              | Key Scale / Attack Rate                    |  |  |  |

| <u> </u>  | KS   /                                           | ´           | AR           | (53, 57, 5Bのaddressは無し)                    |  |  |  |

| 5E        | V                                                |             |              |                                            |  |  |  |

| 60        |                                                  |             |              | Decay Rate                                 |  |  |  |

| :         |                                                  |             | DR           | (63, 67, 6Bのaddressは無し)                    |  |  |  |

| 6E        | <u> </u>                                         | <del></del> |              |                                            |  |  |  |

| 70        | /                                                |             | SR           | Sustain Rate                               |  |  |  |

| 7E        |                                                  |             | OI V         | (73, 77, 7Bのaddressは無し)                    |  |  |  |

| 80        | -                                                |             |              | Outsin Level (Balance Bote                 |  |  |  |

| 30        | l sL                                             |             | RR           | Sustain Level/Release Rate                 |  |  |  |

| 8E        |                                                  | ł           |              | (83, 87, 8Bのaddressは無し)                    |  |  |  |

| 90        |                                                  |             |              | SSG-Type Envelope Control                  |  |  |  |

| :         | /                                                |             | SSG-EG       | (93, 97, 9Bのaddressは無し)                    |  |  |  |

| 9E        |                                                  |             |              | (93, 97, 9B0/8ddressta## C/                |  |  |  |

| A0        | 1                                                |             |              |                                            |  |  |  |

| <u>A1</u> | 4                                                | F-Num. 1    |              |                                            |  |  |  |

| A2        | <del>                                     </del> |             |              | F-Number / Block                           |  |  |  |

| A4        | /                                                | DI OCK      | E Nu 2       |                                            |  |  |  |

| A5        | /                                                | BLOCK       | F-Num. 2     |                                            |  |  |  |

| A6        | <del>                                     </del> |             |              |                                            |  |  |  |

| A8        | -                                                | 3CH*F-Num.  | 1            |                                            |  |  |  |

| A9<br>AA  | -                                                | oon r-wum.  | 1            |                                            |  |  |  |

| AC        | +                                                |             |              | 3CH-3Slot F-Number/Block                   |  |  |  |

| AD        | /   a                                            | CH*BLOCK    | 3CH*F-Num. 2 |                                            |  |  |  |

| AE        | 1/                                               | 220310      |              |                                            |  |  |  |

| B0        |                                                  | · ·         |              |                                            |  |  |  |

| B1        | 1 /                                              | FB          |              | Self-feedback/Connection                   |  |  |  |

| B2        |                                                  |             |              |                                            |  |  |  |

|           |                                                  |             |              |                                            |  |  |  |

## (b) SSG部レジスタ(ライト/リード可能)

| address | Re          | gister         | _                     |  |  |

|---------|-------------|----------------|-----------------------|--|--|

| (HEX)   | d7 d6 d5 d4 | d3 d2 d1 d0    | Comment               |  |  |

| 00      | Fin         | e Tune         | Channel-A Tone Period |  |  |

| 01      |             | Coarse Tune    |                       |  |  |

| 02      | Fin         | e Tune         | Channel-B Tone Period |  |  |

| 03      |             | Coarse Tune    | _                     |  |  |

| 04      | Fin         | e Tune         | Channel-C Tone Period |  |  |

| 05      |             | Coarse Tune    |                       |  |  |

| 06      |             | Period Control | Noise Period          |  |  |

| 07      | IN/OUT /NO  | ISE /Tone      | Mixer Control         |  |  |

| 08      | M           | Level          | Channel-A Amplitude   |  |  |

| 09      | M           | Level          | Channel-B Amplitude   |  |  |

| OA      | M           | Level          | Channel-C Amplitude   |  |  |

| 0B      | Fin         | Tune           | Envelope Period       |  |  |

| OC      | Coar        | se Tune        | <u> </u>              |  |  |

| OD      |             | C ATT ALT HLD  | Envelope Shape, Cycle |  |  |

| 0E      | 1/0         | Port-A         | I/O port Data         |  |  |

| 0F      | 1/0         | Port-B         |                       |  |  |

#### (c) ステータスレジスタ(リード専用)

| address |      | Register |    |    |    |    |    |    | 0       |  |  |  |  |  |

|---------|------|----------|----|----|----|----|----|----|---------|--|--|--|--|--|

| (HEX)   | d7   | d6       | d5 | d4 | d3 | d2 | d1 | ď0 | Comment |  |  |  |  |  |

| XX      | Busy |          |    |    |    |    | FL | AG | Status  |  |  |  |  |  |

#### 2. CPUインターフェース

YMF264内のレジスタへのデータの書き込み及びレジスタからのデータの読み出しは、/CS、/WR、/RD、A0の各コントロール端子によりデータバスのコントロールを行い、データバスにレジスタのアドレスまたはデータを設定することで行います。コントロール端子によりデータバスは以下のようなモードになります。

|   | /CS | /WR | /RD | A0 | モード       |

|---|-----|-----|-----|----|-----------|

| Ì |     |     |     | L  | アドレス・ライト  |

| ı | ъ   | ь   | Н   | Н  | データ・ライト   |

|   | T   | 77  | 7   | L  | ステータス・リード |

| ١ | Ь   | H   | ъ   | Н  | データ・リード   |

| ١ | H   | ×   | ×   | ×  | インアクティブ   |

× : Don't care

#### (a) データの書き込み

レジスタにデータを書き込む手順は、<u>アドレスライトモード</u>でレジスタのアドレスをデータバスに設定し、その後<u>データライトモード</u>でレジスタに書き込むデータをデータバスに設定します。同じアドレスのレジスタには連続してデータのライトが可能です。また、レジスタにデータが確定されるために各モード後に以下の待ち時間が必要です。

#### 1. アドレスライト後のウエイト時間

(unit:s)

|                  | 分周数 | ウェイト時間 |

|------------------|-----|--------|

| SSG音源部           | 2   | 7 × T  |

| アドレス             | 3   | 9.5×T  |

| 00H <b>~</b> 0FH | 6   | 17×T   |

| FM音源部            | 2   | 7 × T  |

| アドレス             | 3   | 9.5×T  |

| 21H~B2H          | 6   | 17×T   |

注) Tはマスタークロックの周期

#### 2. データライト後のウエイト時間

(unit:s)

|         | 分周数 | ウエイト時間       |

|---------|-----|--------------|

| SSG音源部  | 2   | $7 \times T$ |

| アドレス    | 3   | 9.5×T        |

| 00H~0FH | 6   | 17× T        |

| FM音源部   | 2   | 28×T         |

| アドレス    | 3   | 42×T         |

| 21H~B2H | 6   | 83×T         |

注) Tはマスタークロックの周期

#### (b) データの読み出し

レジスタからデータを読み出す手順は、アドレスライトモードでレジスタのアドレスをデータバスに設定し、その後<u>データリードモード</u>にすることでデータバスにレジスタの内容が出力されます。また、アドレスライト後には前ページ記述の待ち時間が必要です。

#### (c) ステータスの読み出し

ステータスレジスタにはアドレスが存在しませんので、<u>ステータスリードモード</u>にすることでデータバスにステータスの内容が出力されます。

#### 3. FM信号音声出力

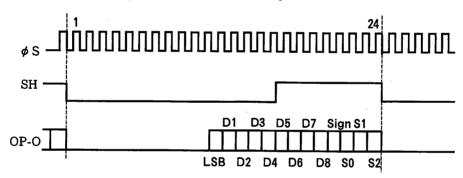

YMF264のFM音声信号はOP-O端子から13ビットのフローティングデータ(仮数部:10ビットLSB-Sign、指数部:3ビット S0-S2)として以下のようなフォーマットで出力されます。このデータをアナログに変換するためにYAMAHAでは、YM3014Bを用意しています。

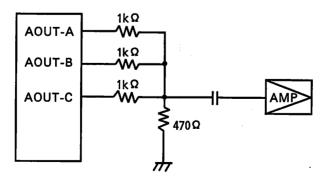

#### 4. SSG音声出力

SSG音声出力信号はAOUT-A~C端子からソースフォロワで出力されます。これをアナログ信号にするには以下のように終端抵抗をつけてミキシングします。

## ■電気的特性

#### 1. 絶対最大定格

| 項目     | 定格值              | 単位 |

|--------|------------------|----|

| 端子電圧   | $-0.3 \sim 7.0$  | V  |

| 動作周囲温度 | 0 ~ 70           | ొ  |

| 保存温度   | −50 <b>~</b> 125 | ℃  |

#### 2. 推奨動作条件

| 項目     | 記号              | 条件 | 最小   | 標準   | 最大   | 単位 |

|--------|-----------------|----|------|------|------|----|

| 電源電圧   | $V_{DD}$        |    | 4.75 | 5.00 | 5.25 | V  |

| 接地電圧   | Vss             |    | 0    | 0    | 0    | V  |

| 動作周囲温度 | T <sub>OP</sub> |    | 0    | 25   | 70   | ℃  |

### 3. 直流特性(推奨動作条件下において)

| 項目          |     | 記号               | 条件                                                     | 最小   | 標準 | 最大   | 単位 |

|-------------|-----|------------------|--------------------------------------------------------|------|----|------|----|

| 入力Highレベル   | 全入力 | $V_{IH}$         |                                                        | 2.0  |    | VDD  | V  |

| 入力Lowレベル    | 全入力 | V <sub>IL</sub>  |                                                        | -0.3 |    | 0.8  | V  |

| 入力リーク電流     | * 1 | $I_{L}$          | V₁=0~5V                                                | -10  |    | 10   | μΑ |

| 出力Highレベル電圧 | * 2 | V <sub>OH1</sub> | I <sub>OH1</sub> =0.4mA                                | 2.4  |    |      | V  |

|             |     | V <sub>OH2</sub> | $I_{OH2}=40 \mu A$                                     | 3.3  |    |      | V  |

| 出力Lowレベル電圧  | 全出力 | Vol              | I <sub>OL</sub> =2mA                                   |      |    | 0.4  | V  |

| 出力リーク電流     | * 3 | IoL              | V <sub>OH</sub> =0~5V                                  | -10  |    | 10   | μΑ |

| アナログ出力電圧    | * 4 | Voa              | 最大音量<br>ミキシング無し<br>R <sub>L</sub> =1kΩ<br>peak to peak | 0.95 |    | 1.35 | v  |

| 電源電流        |     | $I_{DD}$         |                                                        |      |    | 20   | mA |

| プルアップ抵抗     | * 5 | Ru               |                                                        | 60   |    | 600  | kΩ |

| 入力容量        | 全入力 | Cī               | f=1MHz                                                 |      |    | 10   | pF |

| 出力容量        | 全出力 | Co               |                                                        |      |    | 10   | pF |

\*1: øM, /WR, /RD, A0端子に適用

\*2:/IRQを除く出力端子に適用 \*3:D0~D7,/IRQ端子に適用

\*4: AOUT-A, B, C端子に適用

\*5:IOA0~IOA7, IOB0~IOB7, /IC, /CS端子に適用

### 4. 交流特性(推奨動作条件下において)

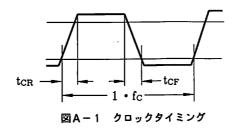

#### 4-1. クロック特性

| 項目            | 記号  | 条件                 | 最小  | 標準 | 最大  | 単位  |

|---------------|-----|--------------------|-----|----|-----|-----|

| 入力クロック周波数     | fc  | プリスケーラ機能<br>(図A-1) | 0.7 |    | 4.2 | MHz |

| 入力クロックデューティ   |     |                    | 40  | 50 | 60  | %   |

| 入力クロック立ち上がり時間 | tcr | (図A-1)             |     |    | 50  | ns  |

| 入力クロック立ち下がり時間 | tcr | (図A-1)             |     |    | 50  | ns  |

#### 4-2. FM音源部

| 項目             |         | 記号                       | 条件                               | 最小   | 標準 | 最大  | 単位 |

|----------------|---------|--------------------------|----------------------------------|------|----|-----|----|

| アドレスセットアップ時間   | A0      | tas                      | (図A-2,3)                         | . 10 |    |     | ns |

| アドレスホールド時間     | A0      | t <sub>AH</sub>          | (図A-2,3)                         | 10   |    |     | ns |

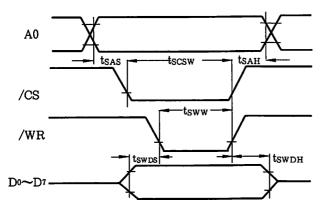

| チップセレクトライト幅    | /CS     | tcsw                     | (図A-2)                           | 200  |    |     | ns |

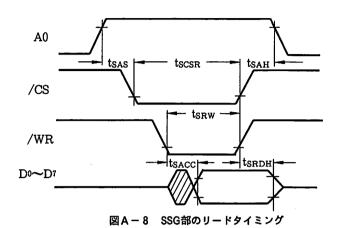

| チップセレクトリード幅    | /CS     | /CS t <sub>CSR</sub> (図A |                                  | 250  |    |     | ns |

| ライトパルス幅        | /WR     | tww                      | tww (図A-2) 200                   |      |    |     | ns |

| ライトデータセットアップ時間 | D0~D7   | twos                     | twos (図A-2) 100                  |      |    |     | ns |

| ライトデータホールド時間   | D0~D7   | twon                     | twDH (図A-2) 20                   |      |    | ns  |    |

| リードパルス幅        | /RD     | trw                      | (図A-3)                           | 250  |    |     | ns |

| リードデータアクセス時間   | D0~D7   | tACC                     | C <sub>L</sub> =100 pF<br>(図A-3) |      |    | 250 | ns |

| リードデータホールド時間   | D0~D7   | trdH                     | (図A-3)                           | 10   |    |     | ns |

| アウトプット立ち上がり時間  | φS      | tori                     | C <sub>L</sub> =100 pF<br>(図A-4) |      |    | 200 | ns |

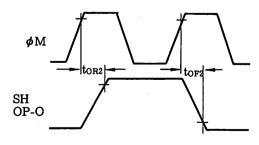

|                | OP-O,SH | ton2                     | C <sub>L</sub> =100 pF<br>(図A-5) |      |    | 300 | ns |

| アウトプット立ち下がり時間  | φS      | torı                     | C <sub>L</sub> =100 pF<br>(図A-4) |      |    | 200 | ns |

|                | OP-O,SH | toF2                     | C <sub>L</sub> =100 pF<br>(図A-5) |      |    | 300 | ns |

4-3. SSG音源部

| 項目             |       | 記号    | 条件                               | 最小  | 標準 | 最大  | 単位 |

|----------------|-------|-------|----------------------------------|-----|----|-----|----|

| アドレスセットアップ時間   | A0    | tsas  | (図A-7,8)                         | 10  |    |     | ns |

| アドレスホールド時間     | A0    | tsah  | (図A-7,8)                         | 10  |    |     | ns |

| チップセレクトライト幅    | /CS   | tscsw | (図A-7)                           | 250 |    |     | ns |

| チップセレクトリード幅    | /CS   | tscsr | (図A-8)                           | 400 |    |     | ns |

| ライトパルス幅        | /WR   | tsww  | (図A-7)                           | 250 |    |     | ns |

| ライトデータセットアップ時間 | D0~D7 | tswds | (図A-7)                           | 0   |    |     | ns |

| ラトイデータホールド時間   | D0~D7 | tswdh | (図A-7)                           | 20  |    |     | ns |

| リードパルス幅        | /RD   | tsrw  | (図A-8)                           | 400 |    |     | ns |

| リードデータアクセス時間   | D0~D7 | tsacc | C <sub>L</sub> =100 pF<br>(図A-8) |     |    | 400 | ns |

| リードデータホールド時間   | D0~D7 | tsrdh | (図A-8)                           | 10  |    |     | ns |

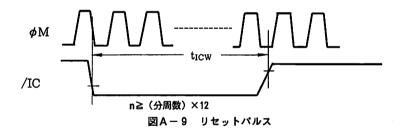

#### 4-4. リセット

| 項目       |     | 記号   | 条件     | 最小     | 標準 | 最大 | 単位 |

|----------|-----|------|--------|--------|----|----|----|

| リセットパルス幅 | /IC | ticw | (図A-9) | 72/fc* |    |    | S  |

\*プリスケーラの分周数に依存する。パルス幅=(分周数)×12

#### 5. タイミング図 (タイミングの設定はV<sub>IH</sub>=2.0V, V<sub>IL</sub>=0.8Vを基準とする。)

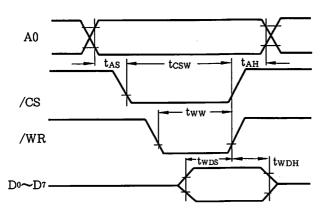

図A-2 FM部ライトタイミング

(注) tcsw. tww, twpH は/CS、/WRの いずれかがHighレベルになった時 を基準とする。

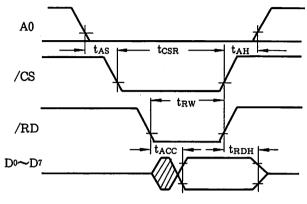

図A-3 FM部リードタイミング

#### (注)

tACCは、/CS、/RDの遅くLow レベルになるのが基準です。 tcsp. tpw. tpppは/CS、/RDの

tcsR. tRW. tRDHは/CS, /RDのいずれかがHighレベルになった時を基準とする。

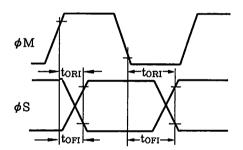

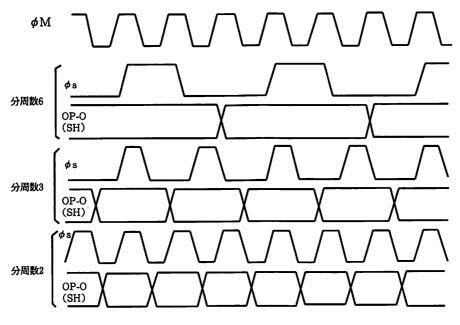

図A-4-a φMとφS(分周数2と3の場合)

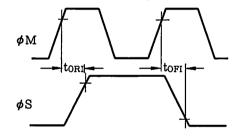

図A-4-b φMとφs(分周数6の場合)

図A-5 φMとSH·OP-O

図A-6 各分周数における \$\phi s \cdot OP-O SHのタイミング

図A-7 SSG部のライトタイミング

#### (注)

tswpsは、/CS、/WRのいずれか遅くLowレベルになる時を基準とする。

tscsw. tsww. tswpHは/CS, /WR のいずれかがHighレベルになった 時を基準とする。

(注)

tsaccは、/CS、/RDの遅くLow

レベルになる時間が基準です。

tscsr. tsrw. tsrdHは/CS, /RD

のいずれかが、Highレベルになっ

た時を基準とする。

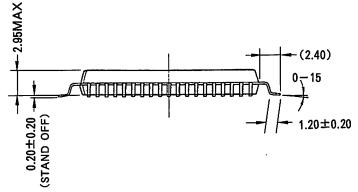

#### ■パッケージ外形図

カッコ内の寸法値は参考値とする モールド外形寸法はパリを含まない 単位(UNIT):mm